# Status and performances of the ARGO-YBJ trigger system

A. Aloisio<sup>1</sup>, P. Branchini<sup>2</sup>, A. Budano<sup>2</sup>, S. Catalanotti<sup>1</sup>, P. Creti<sup>3</sup> and S. Mastroianni<sup>2</sup> for the ARGO-YBJ Collaboration

**Abstract:** The ARGO-YBJ ground-based detector at YangBaJing allows investigating many issues in gamma-astronomy and cosmic-ray physics spanning a large energy range by means of its ability to operate down to a few hundreds of GeV and up to PeV. The apparatus consists of a single layer of about 2000 Resistive Plate Chambers (RPCs) for a total instrumented area of 6700 m<sup>2</sup>. All the detector has been fully equipped with the final front-end, trigger and DAQ electronics and it has been taking data since February, 2007. The detection of small size showers is one of the main task of the ARGO-YBJ experiment. The expected trigger rate due to the cosmic rays is less than 10kHz. In this paper, we present the design and the performance of the trigger system.

## Introduction

The ARGO-YBJ experiment (Astrophysical Radiation with Ground-based Observatory at YangBa-Jing) studies a wide class of phenomena in cosmic rays and astroparticle physics by observing the secondary particles of the atmospheric showers [1]. The energy spectra of the showers of interest span from a few hundreds of GeV to PeV range.

The carpet is made of a single layer of RPCs that work in streamer mode and each chamber is read out by means of 80 pick-up strips. The detector is clustered in 6 x 2-RPC units, named Clusters, with modular read-out and local trigger electronics housed in a Local Station (LS)[2]. In each Cluster the 960 pertaining strips are bundled in groups of 8 in order to form 120 Pads. Each Pad signal latches the binary status of its strips into a register and it is also sampled by a digital multi-hit TDC with a time resolution of about 1 ns. Thus, the detector provides a space-time pattern of the shower front with a very fine granularity.

The detector has been fully equipped with the final front-end and trigger electronic. In this paper we describe the trigger architecture: in particular the shower selection capability and the monitoring

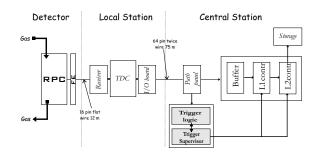

Figure 1: The DAQ scheme.

system that controls continuously the dead time at different levels in the Data Acquisition system.

## The trigger system

As said previously, the DAQ basic detection unit is the Cluster: all the information (time and position) collected and managed by the Local Station is sent to the Central Station for trigger purpose and data read-out. Fig. 1 shows a schematic view of the DAQ architecture. In this paper, we will describe

<sup>&</sup>lt;sup>1</sup>Dipartimento di Fisica, Università "Federico II" and INFN, Napoli, Italy

<sup>&</sup>lt;sup>2</sup>Dipartimento di Fisica, Università Roma Tre and INFN, Roma, Italy

<sup>&</sup>lt;sup>3</sup> Dipartimento di Ingegneria, Università degli Studi di Lecce and INFN, Lecce, Italy Stefano.Mastroianni@na.infn.it

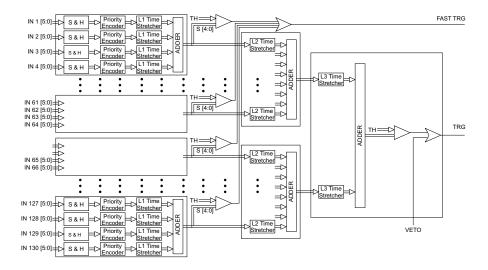

Figure 2: The Low Multiplicity trigger logic

the trigger unit: the trigger logic for the event selection and the trigger supervisor which provides the interface with the DAQ system. The Trigger logic implements two different selection algorithms based on a simple, yet robust, majority logic which takes into account the density and the timing distribution of the fired pads. The Low Multiplicity (LM) trigger implements an inclusive logic to record small-size showers and the High Multiplicity (HM) trigger offers four selection channels to select showers which have a much higher particle density [3].

The LS outputs are the input to the trigger logic: a 6-bit LM weighted bus (when  $\ge 1$ ,  $\ge 2$ ,  $\ge 3$ ,  $\ge 4$ ,  $\ge 5$ ,  $\ge 6$  pads are fired) and a 4-bit HM weighted bus (when > 7, > 16, > 32, > 64 pads are fired).

The LM trigger box processes a total of 130 (clusters) x 6 data bits from the central carpet. The logic shows a three-level architecture (Fig. 2). In this scheme, the Level-0 receives up to 4 LM buses and implements the front-end sample and hold. In order to guarantee the coincidence across 4 clusters (IN1[5:0],..,IN4[5:0]), also in the worst case of hit timing, it stretches the bit widths to about 150 ns. The encoder and adder logic processes the cluster data multiplicities and adds them. Each 4-bus adder generates a fast trigger if the pad multiplicity exceeds the assigned threshold. All the fast trigger signals are put in OR to generate the final trigger

signal. The Level-1 block works in the same way: it stretches the 3 Level-0 output buses to about 250 ns in order to guarantee the coincidence across the 12 clusters. The Level-2 manages the coincidence across 65 clusters (about 360 ns) and, finally, the level-3 block shapes the Level-2 outputs to about 400 ns and calculates the total multiplicity for the entire carpet. If this value exceeds the programmed threshold on the carpet, it generates the LM trigger. The HM trigger logic works in the same fashion and produce 4 trigger proposals.

The LM trigger, the fast trigger and the four HM triggers are put in OR. The trigger logic is divided in 3 VME crates tied by a vertical connection: two for the LM and one for the HM channels. The LM trigger block is now completely installed and functional (with the threshold on the entire carpet set to 20 fired pads).

When the trigger signal is forwarded to the Local Stations, it acts as a common stop for all the TDCs. The local information composed of the TDC output and the patterns of the fired strips is collected and transmitted to the DAQ system at a rate of 20 MB/s and pushed into a FIFO memory placed in the buffer modules of the read-out system. During this transfer, the Local Station continuously asserts a local Busy in order to prevent the generation of further triggers. Its width is proportional to the length of the data frame to be transferred, and it

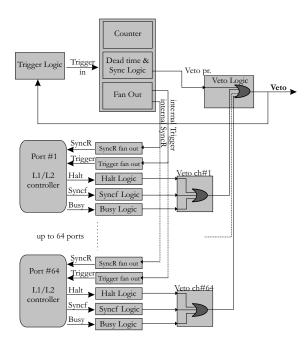

Figure 3: The Trigger Supervisor logic block

changes with the number of the fired Pads in the Cluster.

The DAQ system is based on a modular structure that allows a high speed and efficient data collection [4]. It implements an event-driven data collection by using two custom bus protocols. The DAQ main features are block-oriented data transfer and read-out cycles labelled by an event number. In Fig. 1 a simplified scheme of the data flow is shown: the L1 controllers manage the buffer read-out and, then, the L2 controllers implement the data collection from up to 8 L1 modules. In this context we are interested in the generation of the Busy signals, which originate the DAQ dead time. For our purpose, all the modules can be seen as a FIFO memory and the Busy is active when at least one is full.

Each data buffer stores the Local Station's frame in a FIFO memory, which is available to the L1 controller via a custom bus. The Almost-full FIFO flag is put in a logical-OR with the Local Station Busy to form a board-level Busy. Inside the L1 crate, the L1 controller receives the wired-OR of all the data buffers' Busy signals (crate Busy). The L1 controller builds a new frame and writes it in a

local FIFO memory available to the L2 controller. Also at this level, the Almost-full FIFO flag is put in a logical-OR with the crate-level Busy to form a L1 Busy signal. The L2 controller collects data from the L1 controllers and stores them in the local FIFO, which is read out by a CPU board via the VMEbus. The L2 controller's Almost-full flag represents the L2 Busy signal. The L1 and L2 controllers make their Busy signals available on the front panels. The logical-OR of all the L1 and L2 Busy signals originates the System Busy. Its duty cycle gives us the Dead Time of the data acquisition process.

The DAQ set-up must be organized in order to have a good read-out efficiency in order to keep the dead time as low as possible. While the L1 Busy component due to the data transfer is not eliminable, the L2 Busy is dominated by the CPU read-out. This means that the dead time measurements and their behaviours can be used to estimate and optimize the overall performances.

The Trigger Supervisor (TS) has been specifically designed to monitor all the L1 and L2 trigger and control lines. It measures the duty cycle and frequency of the Busy signals and it generates and distributes the Veto signal to the Trigger logic. In order to be scalable, the TS is organized in a modular structure of VME boards hosted in a dedicated crate with a custom backplane. The TS logic block diagram is shown in Fig. 3.

The TS receives the Trigger pulse from the Trigger logic as an input and distributes it to all the L1/L2 controllers. It also generates and controls the synchronization cycle. All the ORed Busy signals from the DAQ controller are put in OR to generate the global Veto signal which is sent to the Trigger logic to inhibit the Trigger generation. This originates the Dead Time of the apparatus. The TS samples the Trigger rate and the duty cycle and frequency of the Dead Time and writes all the measured quantities in memory banks.

#### The functionalities

Our greater interest is in low-energy showers: we will study the response of the ARGO-YBJ detector to small-size showers with respect to the trigger selection and read-out efficiency. In order to quantify the capability of the ARGO-YBJ detector to trigger

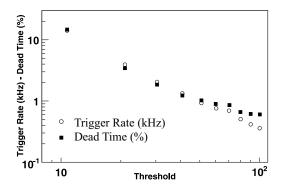

Figure 4: Trigger rate and dead time

on these events it is convenient to measure the trigger rate and the dead time by decreasing the trigger threshold to the lowest acceptable value with respect to the spurious signals of the detector (~400 Hz/pad). Fig. 4 shows the trigger rate and the dead time to different thresholds. The minimum value to reduce the shower noise is 20 pads with a dead time of a few %. From MonteCarlo simulations with a 20-pad threshold we expect a 490 GeV median energy for gamma showers [5].

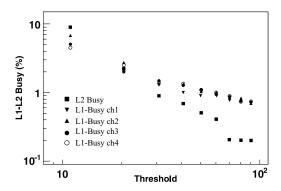

In order to keep the Dead Time as low as possible it is essential to reduce the L1 and L2 Busy, and this in turn requires an effective decoupling between the 3 FIFO levels. In Fig. 5 the measured L1 and L2 Busy components versus the trigger rate is shown. It is evident that all the L1 components are about the same and increase proportionally to the trigger rate. In our set-up (with a 20-pad threshold) with a 4% dead time we measure an average L1 Busy of about 2%. It is important to note that up to 20-pad threshold the L2 Busy component is lower than the L1 components, which means an effective decoupling between L1 and L2 controllers.

## **Conclusions**

The detection of small-size showers is one of the main tasks of the ARGO-YBJ experiment. An inclusive trigger able to record a minimum number of hits has been implemented, based on a four-level coincidence scheme which correlates only signals

Figure 5: The dead time sources

pertaining to adjacent areas. The expected trigger rate with a 20-pad threshold due to the cosmic ray background is less than 10 kHz.

The measurements of the DAQ performances demonstrate that the system is capable to sustain a good trigger rate with a very low dead time.

The Trigger System has shown to be a viable tool to select different-topology shower events and to measure the decoupling between the L1 and L2 FIFOs by measuring the dead time of different channels.

#### References

- [1] D. Martello et al., These Proceedings

- [2] R. Assiro et al., Nucl. Instr. and Meth. A 518 (2004).

- [3] A. Aloisio et al., IEEE Trans. Nucl. Sci. Vol. 51, No. 4, Aug 2004, pp. 1835-1839.

- [4] F. Galeazzi et al., These Proceedings

- [5] S. Mastroianni, Proceedings of the 29th ICRC (Pune 2005), 5 pp.311-314.